TMS320C6657CZHA IC DSP FIX/โฟลตพอยต์ 625FCBGA

พารามิเตอร์ผลิตภัณฑ์

คำอธิบาย

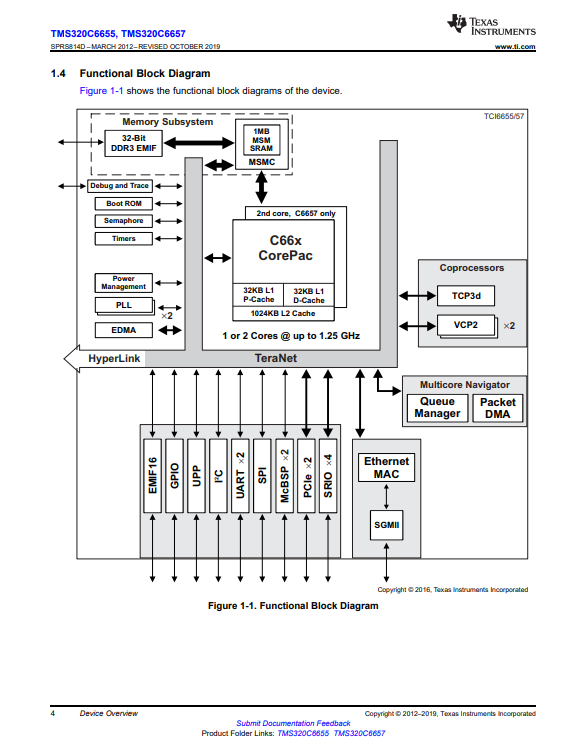

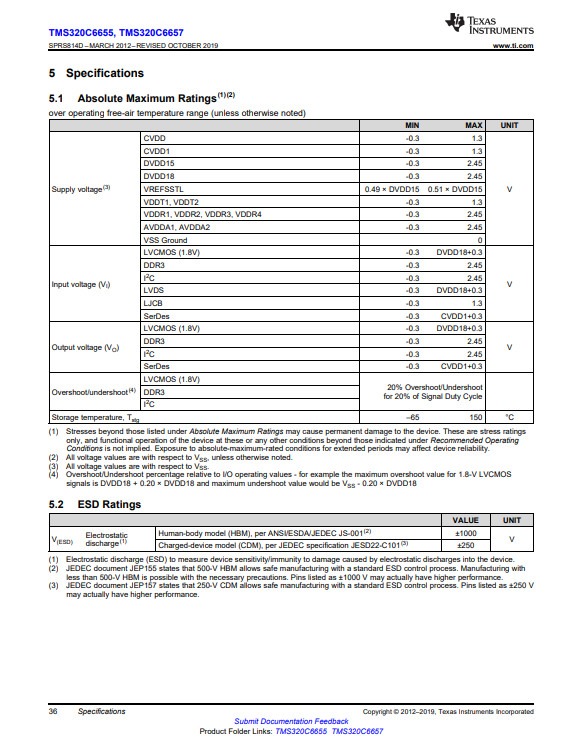

สถาปัตยกรรม KeyStone ของ TI เป็นแพลตฟอร์มที่ตั้งโปรแกรมได้ซึ่งรวมระบบย่อยต่างๆ (คอร์ C66x, ระบบย่อยหน่วยความจำ, อุปกรณ์ต่อพ่วง และตัวเร่งความเร็ว) และใช้ส่วนประกอบและเทคนิคที่เป็นนวัตกรรมใหม่เพื่อเพิ่มการสื่อสารระหว่างอุปกรณ์และระหว่างอุปกรณ์ ซึ่งทำให้ทรัพยากร DSP ต่างๆ ทำงานได้อย่างมีประสิทธิภาพและราบรื่นศูนย์กลางของสถาปัตยกรรมนี้คือส่วนประกอบหลัก เช่น Multicore Navigator ที่ช่วยให้การจัดการข้อมูลระหว่างส่วนประกอบต่างๆ ของอุปกรณ์มีประสิทธิภาพTeraNet เป็นแฟบริคสวิตช์ที่ไม่ปิดกั้น ช่วยให้สามารถเคลื่อนย้ายข้อมูลภายในได้อย่างรวดเร็วและปราศจากความขัดแย้งตัวควบคุมหน่วยความจำที่ใช้ร่วมกันแบบมัลติคอร์ช่วยให้สามารถเข้าถึงหน่วยความจำที่ใช้ร่วมกันและหน่วยความจำภายนอกได้โดยตรงโดยไม่ต้องใช้ความจุของสวิตช์แฟบริคสำหรับการใช้งานแบบ fixed-point แกน C66x มีความสามารถในการคูณสะสม (MAC) 4 เท่าของแกน C64x+นอกจากนี้ คอร์ C66x ยังผสานรวมความสามารถของจุดลอยตัวและประสิทธิภาพการประมวลผลดิบต่อคอร์คือ 40 GMACS ต่อคอร์ระดับแนวหน้าของอุตสาหกรรม และ 20 GFLOPS ต่อคอร์ (@ ความถี่ในการทำงาน 1.25 GHz)แกน C66x สามารถดำเนินการกับ MAC แบบทศนิยมเดี่ยวที่มีความแม่นยำ 8 รายการต่อรอบ และสามารถดำเนินการแบบสองเท่าและแบบผสมได้ และเป็นไปตามมาตรฐาน IEEE 754แกน C66x รวมคำสั่งใหม่ 90 คำสั่ง (เทียบกับแกน C64x+) ที่กำหนดเป้าหมายสำหรับการประมวลผลเชิงทศนิยมและเวกเตอร์คณิตศาสตร์การปรับปรุงเหล่านี้ทำให้มีการปรับปรุงประสิทธิภาพอย่างมากในเคอร์เนล DSP ยอดนิยมที่ใช้ในฟังก์ชันการประมวลผลสัญญาณ คณิตศาสตร์ และการรับภาพแกน C66x เข้ากันได้กับรหัสย้อนหลังกับแกน DSP แบบคงที่และลอยตัว C6000 รุ่นก่อนหน้าของ TI ทำให้มั่นใจได้ถึงความสามารถในการพกพาซอฟต์แวร์และวงจรการพัฒนาซอฟต์แวร์ที่สั้นลงสำหรับแอปพลิเคชันที่ย้ายไปยังฮาร์ดแวร์ที่เร็วขึ้นC665x DSP รวมหน่วยความจำบนชิปจำนวนมากนอกเหนือจากโปรแกรม L1 ขนาด 32KB และแคชข้อมูลแล้ว หน่วยความจำเฉพาะ 1024KB ยังสามารถกำหนดค่าเป็น RAM หรือแคชที่แมปได้อุปกรณ์นี้ยังรวม 1024KB ของ Multicore Shared Memory ที่สามารถใช้เป็น L2 SRAM และ/หรือ L3 SRAM ที่ใช้ร่วมกันหน่วยความจำ L2 ทั้งหมดรวมการตรวจหาข้อผิดพลาดและการแก้ไขข้อผิดพลาดเพื่อการเข้าถึงหน่วยความจำภายนอกอย่างรวดเร็ว อุปกรณ์นี้มีอินเทอร์เฟซหน่วยความจำภายนอก DDR-3 (EMIF) 32 บิตที่ทำงานที่อัตรา 1333 MHz และรองรับ ECC DRAM

| ข้อมูลจำเพาะ: | |

| คุณลักษณะ | ค่า |

| หมวดหมู่ | วงจรรวม (ไอซี) |

| สมองกลฝังตัว - DSP (ตัวประมวลผลสัญญาณดิจิทัล) | |

| ผศ | เท็กซัส อินสตรูเมนท์ |

| ชุด | TMS320C66x |

| บรรจุุภัณฑ์ | ถาด |

| สถานะชิ้นส่วน | คล่องแคล่ว |

| พิมพ์ | จุดคงที่ / จุดลอยตัว |

| อินเตอร์เฟซ | DDR3, EBI/EMI, อีเธอร์เน็ต, McBSP, PCIe, I²C, SPI, UART, UPP |

| อัตรานาฬิกา | 1GHz |

| หน่วยความจำไม่ลบเลือน | รอม (128kB) |

| แรมบนชิป | 2.06MB |

| แรงดันไฟฟ้า - I/O | 1.0V, 1.5V, 1.8V |

| แรงดัน - แกน | 1.00V |

| อุณหภูมิในการทำงาน | -40°C ~ 100°C (TC) |

| ประเภทการติดตั้ง | พื้นผิวติด |

| บรรจุภัณฑ์ / กล่อง | 625-BFBGA, FCBGA |

| แพ็คเกจอุปกรณ์ซัพพลายเออร์ | 625-FCBGA (21x21) |

| หมายเลขผลิตภัณฑ์พื้นฐาน | TMS320 |

ที่เกี่ยวข้องสินค้า

-

โทร

-

อีเมล

-

สไกป์

-

วอทส์แอพ

วอทส์แอพ